Jim Williams had this article in EDN http://www.edn.com/article/465898-JFET_based_dc_dc_converter_operates_from_300_mV_supply.php. This is also referred to as the blocking oscillator. See the link to the wiki section in references below. I had made a variant of this in College as the shocker.

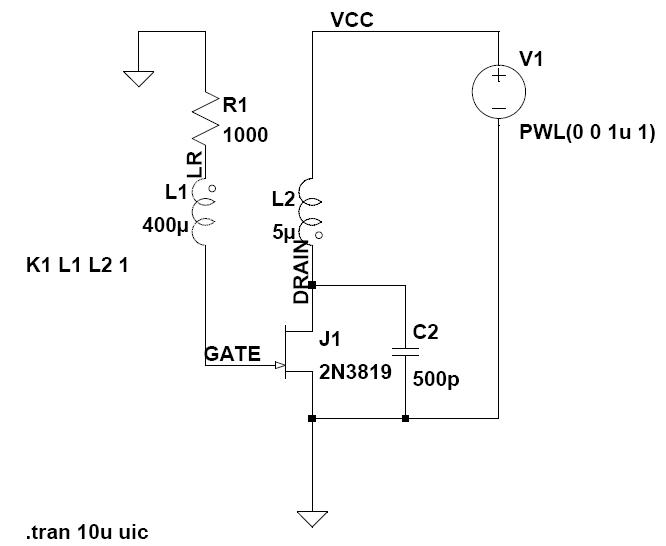

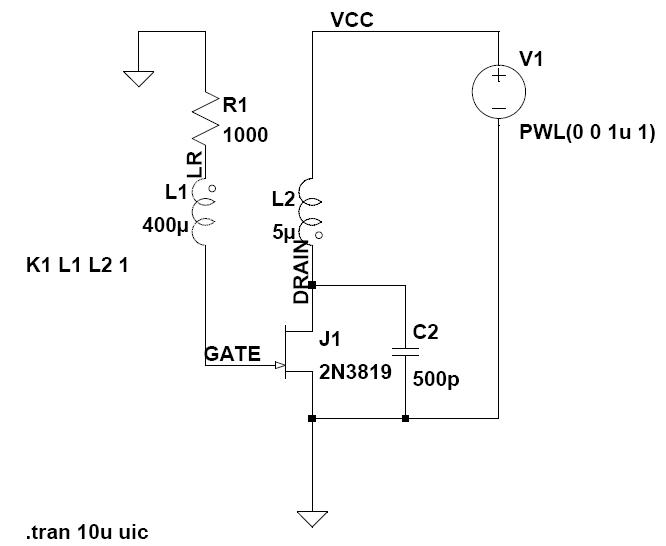

This shows a low voltage JFET oscillator. The basic cell of the oscillator is is:

Making this in LTSpice as:

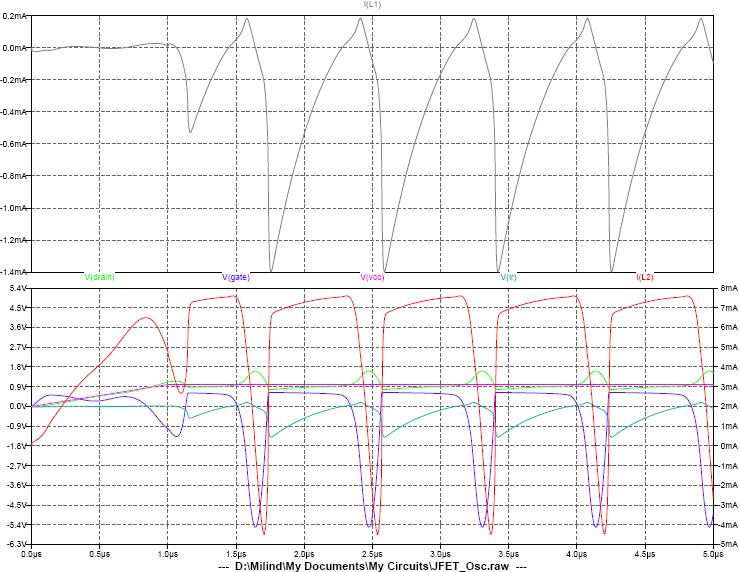

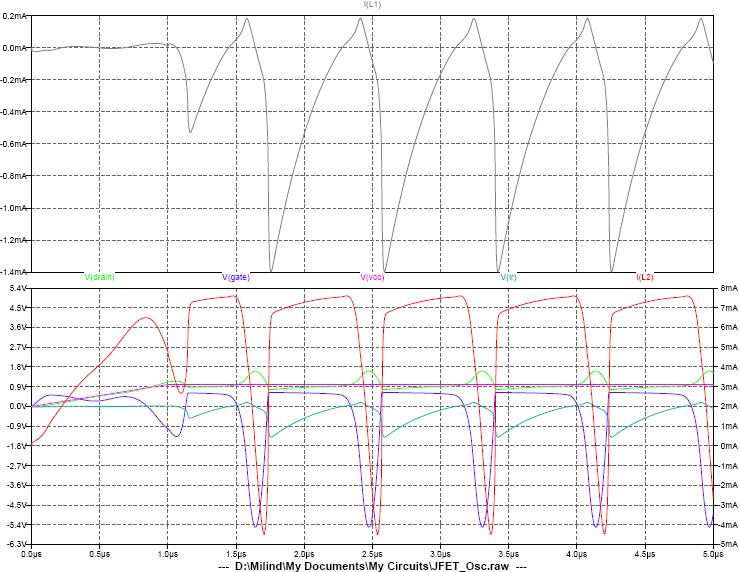

Simulating this the waveforms look like:

Understanding the waveforms:

This shows a low voltage JFET oscillator. The basic cell of the oscillator is is:

Making this in LTSpice as:

Simulating this the waveforms look like:

Understanding the waveforms:

- When Vcc rises the current in L2 rises but it cannot go to 0 immediately when the DRAIN is the same as Vcc, DRAIN rises above Vcc.

- Initially when the voltage across L2 is positive then the GATE is clamped to a diode and the resistor R1 helps limit the current.

- As the Vcc-DRAIN voltage difference decreases the secondary voltage also decreases thus causing the drop across R1 to decrease and the current go to 0.

- As soon as DRAIN rises above Vcc the secondary voltage also reverses causing the current to reverse and the GATE voltage to fall turning off the JFET device.

- On the other hand the reverse voltage on L2 causes the L2 current to reverse and start discharging the DRAIN capacitance until it goes below the Vcc level and the cycle starts again.