Here is a list of all the things to keep in mind while designing test methodologies for Parameters for an IC.

General Points

- The Test setup is a plug in connector with a very bad heat sinking capability so all tests that need to dissipate power must be done in the end and those tests should be carefully designed to minimize the power. The following techniques can be implemented:

- Use a pulsing scheme to allow the part to cool off between measurements.

- Add a test mode to test a scaled down version of the test so that scaled down version of power is dissipated.

- The test setup may have long wires and associated high inductances with the pin connections. Talk to the test engineer about what they can do for very fast timing measurements and pulses given to the chip. Normally the TE was able to measure rise and fall times in the range of nano seconds.

- Not all packages can have Kelvin at all temperatures. So either they get a Kelvin or they get temperature testing. For these type of situations you may have to make temperature testing GBD and create a characterization package.

Switching Regulators

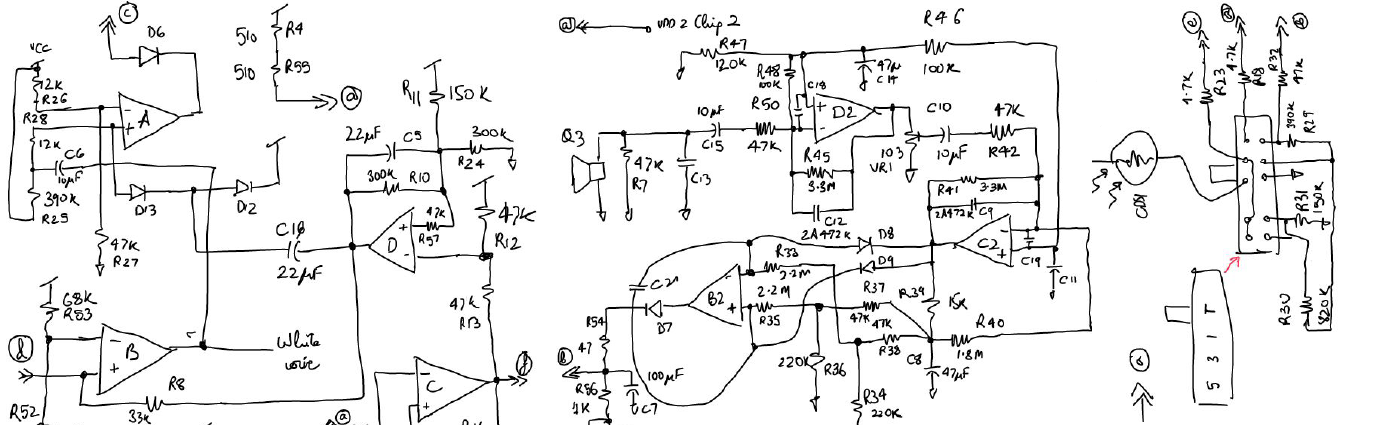

- In some chips we did a in circuit test for the chip i.e. where the tester operates it actually as a switching regulator. In one case we started seeing the problem that in operation the converter started shutting down. One interesting theory we discussed was that since the current sense resistor is after the inductor of the buck (in series with it) and our LX node is switching at the rate of say 5V/ns to trigger the current limit (400mA) we would just need: