A handy list of steps involved as a designer to define, launch, design, test and release new Analog ICs. The list has grown over the years and I still keep adding stuff in it. Comments/additions would be welcome!

Information Management Setup

The 1st step is to create a Information Organization structure on your computer. This is very important since the number of documents, measurements, specifications quickly get overwhelming and hard to keep track of.Directory Structure

- Process Project Directory (To characterize different devices for the process, may be done in product project directory but update the process project directory also)

- Product Project Directory (This depends on your EDA tool and version control system but need to keep this information organized properly)

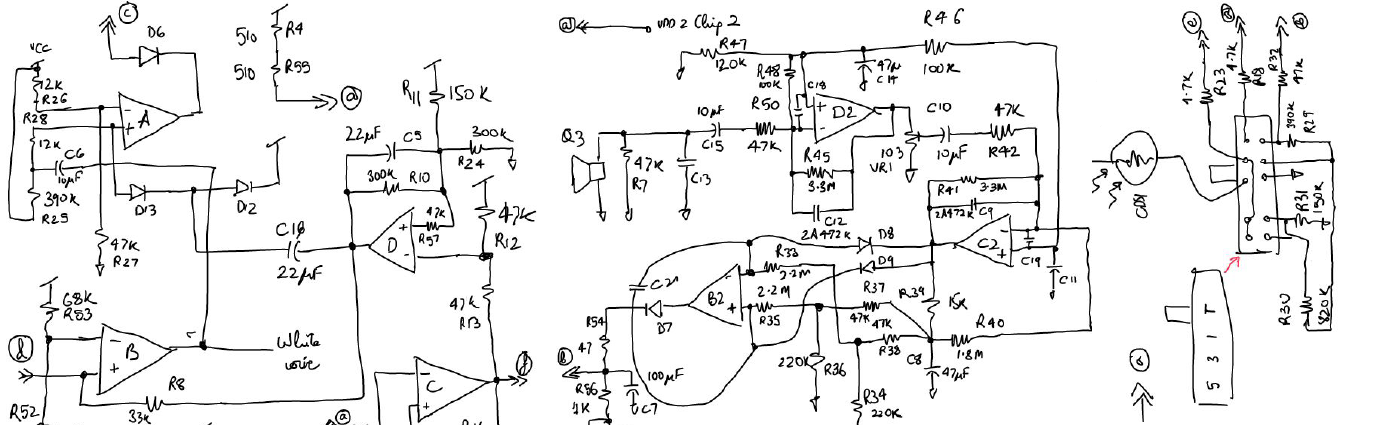

- Schematics

- Datewise Schematic Backups

- Symbols

- Corresponding to Schematics backup

- Simulation Data

- Copy the Netlist file with the simulation results file for reference. This is especially true if the process is new because the models evolve and change over time. Sometimes it becomes very hard to replicate previous simulations.

- Schematics

- Product Folder: Following Subfolders and the timeline and Schedule

- Design Documents: Following subfolders and schematics

- Market Definition: All documents related to Market Definition and Business Manager discussions

- Definition and Specification: Contains all documents pertaining to the definition and initial target specifications - Main document, graphs, drawings

- Simulation results: Any done for the IOS

- Design Review: All documents pertaining to the Design Review - Simulation Graphs, EC Table, Simulation results(Spreadsheet), ESD Files

- Die Size estimate calculations

- Design Notes: This directory generally contains my design spreadsheets, scanned or tablet written design journals. Simulation EC Tables and other working documents.

- Layout: Documents pertaining to Layout - Floorplan, Stream Files, Placement instructions, probe points list and coordinates

- Documents Referenced: Papers, other project Design Reviews, Process Files

- Bonding and Assembly: Bond Diagrams, Assembly Request Forms, etc.

- Bench Testing: Sample inventory directory, Sample Categorization charts, Readings, Graphs, Report

- Tapeout Documents: All documents submitted for Tapeout - Mask ECN, stream file, LVS and DRC reports, etc.

- Project Directory: Copy of the project directory after Tapeout.

- Testing and Wafer Sort

- QA Documents

- Datasheet

- Logistics: To contain tracking of all the parts received and sent etc.

- Design Documents: Following subfolders and schematics

Development Steps

Market Definition

Basic functionality needed by intended customer to be used very easily and tolerable limits should be decided at this stage.- Do a chip feasibility Analysis. For this do the following:

- Read all the information provided carefully and check the basic things like:

- package possibilities currents and the bond wires needed plus the pins you would need, enough pins?

- Specs make sense e.g low shutdown current in a chip with large current? Leakages are higher.

- Spec limits mentioned are testable?

- Create a block diagram for the part functionality with the blocks that can be ported from other parts or created reasonably well. Create list of questions and get them answered so that the block diagram level is finished for the part.

- From the circuit complexity determine the critical points that determine the process requirements like voltage handling capability or speed requirements.

- Try setting specifications for each block: If cannot then assume some numbers. Create a list of critical questions about the specifications which might affect die size and/or process for the part. Get these answered so that you have idea of all critical specifications.

- Get overview of any special ESD robustness requirement.

- Clearly define the ESD objective and make sure the intended processes can support that.

- Define the target voltage (kV) and target specification (HBM, MM, IEC, etc.).

- Create a Die Size estimate for the part

- Create a list of required Wafer Sort and Final Test steps.

- Take All inputs (expectations) from the definer and the Business Manager:

- Estimated Selling Price for the part

- Wafer Cost for processes (intended processes should be listed out first)

- Wafer Sort and Test Cost estimates for the part.

- Packaging Cost.

- Discuss the above results during Market Definition and take inputs from everyone concerned.

- Read all the information provided carefully and check the basic things like:

- The Wafer cost of the process will determine the approximate cost of the chip depending on the die size.

Initial Target Specification

- System Architecture and Macro model

- Create a Block Diagram

- Set Specifications for individual Blocks

- Identify and record all issues for every block This comes out from:

- Market Definition

- System Level Simulation

- Previous Similar Project

- Chip behavior for conditions outside the specifications

- Pick out relevant blocks from other chips.

- Create a System level Macro model to simulate the design. Identify areas of concern and create a brief plan how to verify it in simulation, bench and final test.

- Select a Process (If not already decided in the Market Definition phase)

- Browse through the process. See Getting Familiar with a Process

- Simulate any critical specifications that need to be met in the process, get a reasonable idea on what might be achievable at what area cost.

- Look into ESD resources to see if specs meet and make a detailed ESD plan with ESD cookbook

- Include design of ESD protection in the Design Schedule

- Create the ESD Scheme for all the pins using the process or ESD guidelines.

- Assign ESD library protection cells with appropriate Absolute Maximum Ratings (AMR).

- Define safe ESD discharge path between every pin-to-pin combination.

- Create the ESD Path table and the ESD Cell schematic.

- Estimate the Die Size

- Look into packages that will be good for this - also depends on package testing capabilities of the Test group (e.g. does it offer Kelvin test at all temperatures or not). List out all possible packages with their associated costs.

- Create a layout plan of all the blocks and a preliminary Bond Diagram especially if the part uses large Power MOSFETs. This would give an idea of the bondwire parasitics to associate with the MOS right from the start.

- Keep in mind the issues listed in Step 1

- Add any other issues identified to the list

- Create a sample pinout.

- Finalize the EC Table

- Identify specs of concern and make a plan on how to verify and test them in simulation, bench and final test

- Each test adds a certain time. Normally the test cost estimate is given for 1s test time. Adding a voltage measurement increases test time by 7mS. (Confirm these numbers with the test engineer and be ready with cost adders at definition meeting.)

- Make sure all the spec limits are testable

- Create the Final Test and wafer sort Section

- List everything tested at Wafer sort with method (mini WS document) with the required pin conditions and method.

- List everything tested at Final Test with method (mini FT document) with the required pin conditions and method.

- List all parameters that will be Guaranteed by Design (GBD)

- Go through the Things to keep in mind for IC Final Test list.

- List out all required Road tests and Typical Operating Curves (TOCs) for the Datasheet

- List out all the Simulation Waveforms Application and Definer need to see in Design Review (DR).

- Write down the detailed description for the blocks and the chip functionality

- Create the Schedule

- Make definition document based on the above analysis, specifying closely what you will achieve

- Send the definition document out 1 week before at least to the Test Engineering.

- Create the Schedule and send it out to test for feedback and approval.

- Definition Meeting and submission

- Schedule the Definition meeting.

- Complete the Definition Action Items

- Send the document by email to all concerned for final review

- After approval ask for die type allocation

- Get the approvals and archive the document

- Get and fill out any cost analysis that needs to be done and submit to Business manager with schedule so that the project can be launched

- Study of Process in detail (2 days)

- Familiarize with all supporting docs

- Collect all matching data (Data Genie and Model Files)

- Go through all electrical specifications

- Refer to Getting Familiar with a Process

Design

- Good idea to follow the Top Down Design Methodology as described By Ken Kundert - The Designer's Guide to Verilog-AMS: 1st (first) Edition

- Design all blocks simulating every corner for each block separately (NOTE: CORNER SIMULATIONS OF SMALLER BLOCKS SHOULD BE A SUPERSET OF CORNER SIMULATIONS OF UPPER LEVEL BLOCKS)

- Have hand analysis of

- Gain of every amp

- GBW Product of every Amplifier in feedback

- Offset of every diffamp

- Accuracy of every current mirror

- Accuracy of all important signals such as the bandgap voltage

- Headroom limits in every circuit

- Over the years I have developed a spreadsheet which does a lot of hand analysis for standard blocks for me taking basic device simulation data.

- Have hand analysis of

- Precautions and Guidance (Make a Caution List for the product, to keep watch all through the development cycle)

- Look up PU/PD issues with your circuit

- Find any high impedance nodes that might stray during power down.

- Look for Latchup sensitive areas of your circuit

- All I/O blocks - I/O defined as diffusion connected to Pad or to any node that basically can go above and below the supply rails and provide good amount of current.

- Specify gaurd rings for layout around any diffusion that is going to pad

- Refer Latchup Safe Design Tips

- Look up matching sensitive areas of the circuit and see if you are safe with mismatches

- Look up layout sensitive interconnects and components and add proper layout notes. See Layout Notes on Schematics for guidelines on layout notes.

- Look up design mistakes history and confirm that you are not repeating any

- Consult senior designers about your new topologies

- Always have a plan to layout any circuitry you design.

- Look up PU/PD issues with your circuit

- Add Shutdown Circuitry to all the blocks if required

- Mark all the high impedance nodes in all blocks

- Make sure all high impedance nodes are set to a rail in shutdown.

- Metal Line widths

- Use the current rating of the wires as an initial estimate

- Separately route all high current carrying lines and connect them to pad using star connection.

- Mark interconnects whose layout resistance will be critical

- Measure current in the Bandgap ground or any critical voltage reference circuits and make sure its voltage drop <1mV with all the metal resistance.

- ESD and Latchup Design:

- Verify design has robust ESD discharge path for every pin-to-pin combination.

- Create ESD protection plan summary.

- Complete the ESD Pin Classification Form.

- Write layout notes for Latch-Up protection on devices going directly to pins.

- Review ESD Design

- Simulation Guidelines

- Pinout and Chip size Estimate

- Populate all cells in a layout and place them

- Do a DFMEA analysis to check for:

- Fire hazard conditions

- Any critical conditions that can be avoided

- Get a layout engineer to start working on the layout around 2 weeks before the Design Review.

- Make the Wafer Sort methodology and send it to the Wafer Sort Engineer

- List All test details (Make schematics if necessary)

- Make the Final Test methodology and send it to the test engineer.

- List All test details (make schematics if necessary)

- Decide the final test temperature

- If using a one time programmable kind of memory then keep in mind that at higher temperature the memory may be programmed weakly since the Ids is less of the floating gate transistor and hence less HCI current.

- Go through the Things to keep in mind for IC Final Test list.

- Create detailed plan of layout of critical circuits.

- Review the latchup guidelines for the process and add important latchup prevention notes.

- Do the write up of the design review document (Not necessary to include the sims, can be added in the week before the design review after sending out the "preliminary" DR document)

- Add layout plan of critical circuits.

- Review Caution List

- Update the floorplan completely.

Design Review

- In your copy of schematics mark all the offset contributions of different components in all diffamps or error contributions in all accurate circuitry

- Look at the Design Reviews points to have all information handy.

- Action Items and submit to Document Archive

Layout

- Reveiw Caution List

- Floorplanning

- All pads should be visualized as contacted by probes. Those visualised probes should not shadow any laser trim resistors.

- Check if there are any violations to the Laser Power adjust resistor placement and the Laser Focus placement

- Update metal widths for all lines now considering the resistance of the lines

- Get a preliminary bond diagram and get it approved

- Placement

- Visualize important analog signal routing and see noise or cross coupling issues

- Visualize Ground and supply routing and see noise or cross coupling issues

- After a block is placed insert at much spare things you can to utilize any possible space wastage.

- Routing

- Mark entry poins of VCC, GND and any other important signals on all blocks and based on those create a top level routing plan for those signals.

- ESD Layout Guidelines

- Verify all Bus resistances are under the expectations of the ESD cell proper functioning.

- Make sure the Layout is Latchup robust:

- Starting with pads highlight all points where the pad connects to diffusions through resistance lower than to cause low drop with 100mA current (JEDEC requirement to pass Latchup).

- Starting with that diffusions get the PNPN structure ending in another pad or supply terminal.

- Draw the parasitic SCR and identify the parasitic Bipolar bases and the biasing resistances. Lower Betas of the bases by adding a guard ring there (guard ring is actually a diffusion we give to the parasitic SCR but reverse the polarity from what was supporting latchup, so now the parasitic SCR does get a diffusion which is first of all a dummy diffusion and then it has reverse polarity) or reduce the biasing resistance by adding taps right at the base of the parasitic bipolar.

- Less Headache method would be to surround the diffusion connected to pad with appropriate guard ring always

- For any N diffusion (N-WELL) connected to GND and any P-Diffusion (P-WELL) connected to the supply should be guard ringed very well since its easier to fwd bias them and turn ON junctions that are close by.

- Bond Diagrams and their approval (Assembly form)

- If using laser trim components make sure to get laser/test plot approval

- Layout Checking

- BLOCK LEVEL:

- Check for placement and orientation of MOS, Bipolar, Resistors

- Lines Routing

- Highlight matched pair lines and make sure the via structure and lengths match.

- Highlight high current lines

- Check for total line resistance seen by the current flow to current consuming devices. Check if vias and line widths are adequate (according to electromigration rules 㠴aken from Layout Design Rules Document).

- Check and mark appropriate point of entries of the top level lines into block.

- Highlight Supply and Ground lines for the block

- Check if any thin links are connecting big islands where more current may be required.

- Mark point of entry of the Supply and Ground lines for the block to get guidance for top level routing.

- Highlight high voltage lines and Metal 1

- Check if high voltage Metal 1 runs across

- EPI pockets

- P Wells

- P Active

- N Active

- If yes then the channel stops must be drawn i.e. p+/n+ rings with contacts around the wells

- Check if high voltage Metal 1 runs across

- Highlight Sensitive lines

- To reduce capacitance to other lines make separation from adjacent line 2x the width of your line

- Check if any noisy lines run close to sensitive signals such as bandgap

- Make sure they do not merge with high current lines to shift their levels.

- Review cross-coupled lines of a R-S latch. Make sure they do not run long or close to noisy lines since if they get a glitch and switch the latch it may be a bad error.

- Review the lines connected to NAND and NOR gates for the coupling induced in them. Example in a NAND gate with 2 series connected NMOS devices, if the lower NMOS is switching quite often the source of the upper NMOS is moving up and down with it coupling noise into the other signal, if we had placed this switching signal on the upper NMOS then the coupling would reduce since it has to go through the Cgs and then the Cgd of the lower NMOS.

- Check if metal lines overlap matched devices unsymmetrically - fix those.

- Highlight all Pocket node lines, NACT, CONTacts, Metal 1 and EPI pockets and check if adequate pocket taps are present.

- Highlight all PWELL node lines, PACT, CONTacts, Metal 1 and PWELLs and check if adequate PWELL taps are present.

- Highlight the EPI pockets in solid color (Different voltage EPIs in different colors) and highlight the P+ in a separate color (solid) to see if all the EPI pockets have a P+ channel stop drawn around them especially around high voltage pockets. Also highlight metal 1 to make sure all P+ channel stops have contacts on them wherever possible.

- For all I/O cells make sure they are Latchup safe. Review the Latchup prevention guidelines set by the ESD group.

- TOP LEVEL:

- Highlight all sensitive lines and try to group them together at maximum places and then run the group between supply/ground lines.

- Check lines overlapping blocks and check any possible coupling effect into block components if metal layers close. Make use of sparser routings in higher metals to separate the lines in a metal layer for minimum coupling.

- Check if metal lines overlap matched devices unsymmetrically - fix those.

- Highlight GSUB and make sure GSUB taps are present sufficiently across the chip and near all circuitry especially around circuitry connected to pads to prevent latchup.

- Highlight the ground lines one by one and make sure their pickups from blocks and resistance is fine. Calculate current through all ground lines and then decide on worst case resistance allowable in the lines.

- Highlight the supply lines and check their distribution to all blocks and whether they are entering the at the point of entries marked during block level review.

- Check for proper metallization thickness on ESD paths.

- Check power bussing to ALL blocks. Check bus width and # of vias used when bus is jumped.

- Check that blocks that need separate supplies are not shorted to other supplies.

- DRC

- LVS

- Reports generation:

- DRC

- Antenna Rule Check

- Assembly rule check

- Density reports

- LVS Soft

- LVS Hard

- XOR (if a die revision)

- PREPBIAS

- Reticle Frame

- Beam

- Fracture and tapeout Data

- Check the fracture report to know how many die per wafer and show the die map.

Tapeout

- SLP checklist

- Generate Burn-In or DOPL Schematic (With ESD Pin Classification)

- Complete the ESD checklist for the part.

- Generate the DFMEA (Design Failure Mode Error Analysis) document if required.

- Wafer Allocation

- find out if the package assembly needs full wafer or cut will do? If full then allot wafer to be packaged

- allot wafer for your local assembly

- Wafer Start Request Form (WSRF) - Start the calculated number of wafers (Ask how many die needed for product release). NOTE: Lot number assigned in WSRF when the formed is signed off completely.

- Mask ECN (Attach documents)

- Reports

- Assembly form approved

- SLP checklist

- Reticle Map

- Wafer Map

- Archive Schematics (procedure on the CAD home page - Archive link)

- Maskview (Optional)

Post Tapeout Until Wafer Ship

- Create a bench testing plan and initiate any test board layout. For example if the test engineer is using a Kelvin socket and you need to correlate properly most likely you need a board with that kelvin socket for correlation. Get that started for layout and fabrication also. See Evaluation Board Design

- After a week or 2 start a Backup lot for the product (Optional - if confident product will work)

- When the wafer out date from the Fab is coming close (~2 months) update the Test and Wafer Sort Engineer on it.

- Attend the Wafer Sort TDR and Final Test TDR. Remember you have to duplicate the setups on bench for correlation.

- Carefully go through each test and its setup. (Check for any possible conflicts to interfere with the measurement targeted for a particular parameter)

- Things you should keep in mind for the TDR:

- All package information (Exposed pad or not, etc.)

- All Schematic connections.

- Decide how many wafers to put through sort/Assembly and FT, do not use all since that takes a lot of time. Just allot enough to have 5K units, with some margin so like 10K is a good number.

Testing Steps

- Get the wafer/samples

- Create a Bond Diagram for Local Assembly.

- Make sure you receive some samples for local assembly

- Receive wafer (from wafer dispatch) and get local assembled or ask sort engineer to do it for you.

- Bond diagram redone to get probe pads out if needed

- Bench Testing

- First of all do a "Wiggle" test - Test operation at various supplies and conditions to get an overview of all functionality and if everything seems to be working and what are the kinks that need to be investigated carefully.

- Create a Test plan

- Make a part organization system

- Store the parts carefully to repeat observations

- Associate observations with each sample (numbered with reference numbers) in a detailed excel sheet

- Go through the full EC Table and note all readings and verify all functionality, you will be asked again and again what you expected in the readings and what did you get, when the apps guy does his road test and the test engineer is getting his hardware ready.

- Create the full readings spreadsheet.

- Make sure for QA Burn In the Burn In board schematics are correct and setup is functional on bench (especially the packaged pin outs).

- Here is a checklist of all that should be done on the bench for evaluation:

- Bench Testing of the part

- Test Development/Correlation

- ESD Test

- Latchup Test

- Mini Burn-In

- Tester Temperature characterization

- Wafer Sort and Correlation

- After the sort engineer gets the Wafer sort done with the correlation units (min 10) ready, perform the correlation on the samples (min 3) locally assembled.

- During correlation look at the kind of sigmas you are getting for the 10 parts. Look for any anomalies and unexpected high sigmas and try to fix them now rather than in GBD stage since it may require correlation again.

- Follow up with the Product Lead Manager (PLM) and Wafer sort engineer to get the sort done on the decided quantity of wafers.

- Assembly

- Follow up with PLM to stay updated with the arrival of the assembled units.

- Get a correlation board ready with a plug gable socket. If Kelvin contacts needed make arrangements for a board to support that.

- Keep the Final Test engineer in the loop of the assembled units arrival, the FT program and hardware should be ready by that time.

- Final Test and Correlation

- After the assembled units arrive, do the test correlation on the parts.

- If the Test hardware is not ready then do a reverse correlation (Do your measurements and ship the units to the Test Engineer to correlate)

- During correlation look at the kind of sigmas you are getting for the 10 parts. Look for any anomalies and unexpected high sigmas and try to fix them now rather than in GBD stage since it may require correlation again.

- Limits and GBD Verification

- The units should be fully characterized. Characterize at least 150 units for proper sigma measurement. Work with the test engineer to refine the tests whose sigmas are large etc.

- Set EC Limits using the GBD sheet.

- When setting limits in summary be sure to look at sigma to be sure it makes sense. Do a histogram plot of the parameter to make sure it is a normal (Gaussian) distribution for sigma to make any sense.

- Discuss the GBD limits with Business Manager and Applications and get their approval if the Datasheet ECN meeting is already held or will be held later.

- GBD Verification is run by the test engineer. Ask the TE to collect all data at all temperatures to provide a copy to you so that if any limit change is requested later on you have the GBD Verification data to analyze the effect.

QA

- After the FT program is ready and correlated, the FT engineer can provide serialized samples to the QA/ESD testing personnel.

- Make sure for QA Burn In the Burn In board schematics are correct and setup is functional on bench (especially the packaged pin outs).

- Verify the ESD Pin classification table is correct and is used for ESD testing.

- Also get the Latchup testing done, if the part is for automotive use then the latchup testing needs to be done at 125C for AEC qualification.

- Latchup Testing

- ESD Testing

- PRECON - (Solder Reflow Preconditioning)

- DOPL Test - (Dynamic Operating Life)Burn in on application board at 125C with no humidity

- HALT - Burn in at 85C of the application board with 85% humidity

- HTRB - (High Temperature Reverse Bias Test). Reverse bias major power handling junctions of the device. Devices are operated in a static operating mode at or near maximum breakdown voltage and or current levels. PI Biases the pins at 80% of the maximum junction breakdown. Also the biasing has to be done to make it static.

- THBT - (Temperature Humidity Biased Test) - For non-hermetic packaged devices operating in humid environments. Accelerates the penetration of moisture through the external protective material. 85% RH at 85C. (PI runs at 100V rather than max voltage)

- HTSL - (High Temperature Storage Life) - Also called stabilization bake test. 150C or 175C.

- MSL - (Reflow Moisture sensitivity) - To classify the sensitivity of non-hermetic sold state SMDs to moisture induced stress so they can be properly packaged, stored and handled. The MSL Soak Requirements table shows the amount of moisture soak time according to the MSL level.

- HAST - (Highly Accelerated Stress Test) - HAST is performed for the purpose of evaluating the moisture resistance of on-hermetic packaged devices operating in high humidity environments. Bias is applied minimizing current draw using alternating potentials wherever possible. The test approximates a highly accelerated version of

Datasheet

- Follow up on the road tests for the graphs to be included in the datasheets, the customer apps engineer should give a report on the tests.

- Review Datasheet manuscripts carefully and attend datasheet meeting.

- Attend and update the limits in the Datasheet ECN meeting.

Transfer to Production

- Transfer test hardware at the final assembly house

- Send a a qual lot to test and correlate with the main test hardware at test development. (This has to be done 3 weeks before to make sure enough time to correlate and debug the test hardware)

Fab Transfer

- Test all the tests not tested in production testing like:

- The thermal shutdown thresholds.

- Bandgap TC i.e. the magic voltage

Glossary

- DOPL Test - Burn in on application board at 125C with no humidity. See Reliability Stress Tests Descriptions.

- HALT Test - Burn in at 85C of the application board with 85% humidity. See Reliability Stress Tests Descriptions.

References

- Portable Power website (Product Development steps)

- Standard Products Website

- Document Control

- Evaluation Board Design